# A study aimed at characterizing the interfacial structure in a tin-silver solder on nickel-coated copper plate during aging

D C LIN1, R KOVACEVIC1, T S SRIVATSAN2\* and G X WANG2

<sup>1</sup>Research Center for Advanced Manufacturing, Department of Mechanical Engineering, Southern Methodist University, 1500, International Parkway, Suite No. 100, Richardson, Texas 75081

<sup>2</sup>Department of Mechanical Engineering, The University of Akron, 302 E, Buchtel Avenue, Akron, Ohio 44325

e-mail: tsrivatsan@uakron.edu

**Abstract.** This paper highlights the interfacial structure of tin-silver (Sn-3·5Ag) solder on nickel-coated copper pads during aging performance studies at a temperature of 150°C for up to 96 h. Experimental results revealed the as-solidified solder bump made from using the lead-free solder (Sn-3·5Ag) exhibited or showed a thin layer of the tin–nickel–copper intermetallic compound (IMC) at the solder/substrate interface. This includes a sub-layer having a planar structure immediately adjacent to the Ni-coating and a blocky structure on the inside of the solder. Aging performance studies revealed the thickness of both the IMC layer and the sub-layer, having a planar structure, to increase with an increase in aging time. The observed increase was essentially non-linear. Fine microscopic cracks were observed to occur at the interfaces of the planar sub-layer and the block sub-layer.

**Keywords.** Interconnections; printed circuit board; electronic packaging; solder bumps; thermal aging performance.

### 1. Introduction

The electronic industry is consistently seeking for advanced, genuinely innovative, interconnection technologies for components and fabrication of printed circuit (PC) boards for large-scale manufacturing. The solder bump flip-chip technology (Andy 2005) has been widely used for components to interconnect, both electrically and mechanically, to the substrate through the solder bumps (Lau 1995; Lau & Erasmus 1993). These interconnections are easily formed in an area on the surface of the printed circuit (PC) board. In this area, or region, an under bump metallurgy, referred to henceforth as UBM, facilitates in the formation of a bond that is receptive to soldering. The nickel coating in the under bump region (UBM) acts as a barrier for the occurrence of diffusion between copper and the solder. In essence, (a) the overall quality of the solder bump, (b) the bond of the solder, and (c) the intrinsic properties of the

<sup>\*</sup>For correspondence

solder/substrate interfaces, are both important and essential for long-term product reliability analysis. In the fabrication of electronic packaging, the manufacturing of printed circuit boards (PCBs) with connection bond pads is critical from the standpoint of reliability. A typical under bump region (UBM) essentially consists of three layers: (i) a copper base layer, (ii) a nickel layer, and (iii) a thin layer of gold (Andy 2005). The thin layer of gold on top of the pad helps in facilitating protection against both corrosion and oxidation of the connection pads. A thin layer of nickel on the copper base helps in slowing down the diffusion of copper into the solder with the purpose of limiting the copper-rich, tin-copper, and the scallop-like intermetallic compounds at the interface of the solder with the substrate.

Gold is well known to have a high dissolution in molten tin-dominated solder. For example, approximately 18 wt% of gold at the soldering temperature (225–250°C) can be dissolved into tin-dominated solder (Ochoa *et al* 2003). This is one of the key advantages in using gold during a reflow process. The nickel layer tends to interact directly with the molten solder once the gold has dissolved. This results in the formation of a sound metallurgical bond between the solder and the pad. Formation and presence of the intermetallic compounds at the interface of the solder and the substrate is considered necessary for a sound solder joint (Tu *et al* 2003). The types of intermetallic compounds formed and their resultant growth are critical to the overall reliability of electronic products.

This paper attempts to focus on the interfacial structure of a Sn3·5Ag solder on nickel-coated copper pads, which find extensive use in packaging assembly. A homogeneous thermal aging process was performed for studying and rationalizing the growth behaviour of the Sn–Cu–Ni intermetallic compound at and near the interface.

# 2. Experimental procedures

## 2.1 Fabrication of solder bumps

The materials used in this study include: (i) A commercial no-clean Sn3·5Ag solder paste. (ii) A PC board having copper bond pads covered with an electroplated Ni/Au coating.

A thermocouple was positioned in the solder paste so that any temperature variations with respect to time, during the reflow process, can be detected and monitored. The board has around forty numbers of the Cu/Ni/Au pads arranged in four rows, with each row having at least ten pads. The procedure used to produce the solder bumps for further analysis is:

- (a) Using acetone solution the connection pads and the stencil were thoroughly cleaned.

- (b) Print solder paste on the connection pads using a stencil. The depositions of a near uniform solder volume, without appreciable misalignment, bridging, or missing bumps, is the desired objective. The overall uniformity of the solder deposit is critical to the overall quality of the assembly. This uniformity is related to both the type of solder paste used and the print process parameters. The volume of solder deposit depends upon the following:

(i) size of the stencil, (ii) thickness of the stencil, and (iii) size of the connection pads.

- (c) The stencil is removed with care.

- (d) Reflow of the solder paste was initiated on a temperature-controlled hot plate in a controlled environment with the peak soldering temperature reaching as high as 250°C.

- (e) When the peak temperature was reached, the coupon was immediately removed from the hot plate and placed in ambient air (298 K) with the purpose of facilitating rapid solidification of the molten solder. The cooling rate was estimated to be about 15°C/sec. The solidified coupon was subsequently taken to a clean facility to enable in the removal of the flux and residue from the solder bumps.

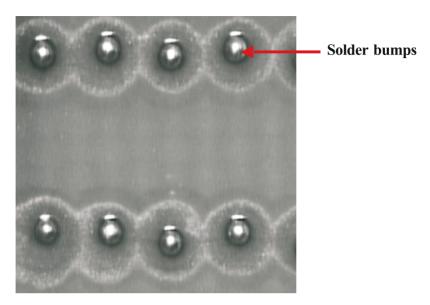

Figure 1. An overhead view of the solder bumps on a printed-circuit (PC) board.

(f) The as-solidified solder bump is shown in figure 1.

### 2.2 Homogeneous thermal aging performance

The as-solidified solder bumps were then placed in a furnace whose temperature was maintained at 150°C. The samples were left in the furnace for four different time intervals: 24, 48, 72 and 96 hours. During the aging process, the solder bumps were subjected to the following:

- (i) A heating process (from room temperature (25°C) to a homogeneous 150°C).

- (ii) An aging process (at 150°C at the four different time intervals).

- (iii) A cooling process (from 150°C to room temperature).

# 2.3 Sample preparation for microstructure analysis

Cross sections of the as-solidified and aged solder bumps were prepared for micrographic examination using the standard metallographic technique. The ground and polished samples were subsequently etched in a solution mixture of 25% nitric acid, 2% hydrochloric acid and 93% methanol. The resultant microstructure of the interfacial regions was examined in a JEOL scanning electron microscope (SEM) in the backscattered mode. The distribution of key elements at the interfacial region was analysed with the aid of energy-dispersive X-ray spectroscope (EDS).

To prepare the coupons for observation in the scanning electron microscopes, the following procedure was used to protect the solder bumps from detachment:

- (a) Graphite was initially applied as a dry film spray lubricant over the solder bumps.

- (b) The entire solder bump was wrapped in an aluminum foil with the purpose of securing each of the solder bumps connected to the neighbour bump.

(c) The solder bumps were cold mounted using a mixture of resin and hardener at the center of the solder bump. This was followed by standard metallurgical preparation of the samples for observation in the scanning electron microscope.

#### 3. Results and discussion

## 3.1 Microstructure of as-solidified Sn3·5Ag solder bump

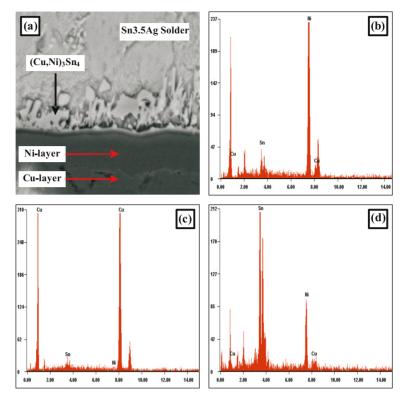

A typical cross section of an as-solidified solder bump is shown in figure 2. The magnified details at the interface between the solder and substrate of the nickel-coated copper pads are shown in figure 3. In figure 3a backscattered electron micrograph is shown, taken at the solder/substrate interface. Figure 3b reveals the distribution of key elements in the nickel-layer through EDS analysis using the point mode technique. Figure 3c reveals the key elements in the copper-layer while figure 3d is an EDS of the Sn–Cu–Ni compound. The distribution of key elements was obtained using the attached X-ray detector with analysis made possible using the EDAX software. The elements present in the various layers are summarised in table 1.

From both figure 3 and table 1, it is observed that the composition of the Ni-layer shows a distribution of 91.08% Ni, 4.17% Sn and 4.75% Cu. Further, in this layer, both tin and copper are believed to come from the neighbouring solder and the copper-layer. In the copper-layer, the EDS analysis shown in figure 3c reveals a distribution of 96.07% Cu, 1.24% Ni, and 2.69% Sn. Further, in this layer the nickel and tin are believed to come from the neighbouring nickel layer and the solder by way of diffusion. On the solder side, i.e. near the solder/substrate interface, EDS analysis revealed (figure 3d) a distribution of 60.86% Sn, 33.72% Ni, and 5.42% Cu. This indicates the presence of the Sn–Ni–Cu ternary phase at the interface. This was identified to be the (Ni<sub>x</sub>Cu<sub>y</sub>)<sub>3</sub>Sn<sub>4</sub> in the published literature (Kang *et al* 2002).

From the data summarised in table 1, it is observed that the amount of copper in the nickel-layer (4.75%) is far more than the amount of nickel in the copper layer (1.24%).

**Figure 2.** Cross-section view of a single solder bump.

**Figure 3.** Backscattered SEM image and EDS analysis for the Sn3·5Ag solder bump. (a) Interfacial structure, (b) EDS map of the nickel layer, (c) EDS map of the copper layer, (d) EDS map of the Sn-Ni-Cu compounds.

This suggests that the copper readily diffuses more atoms into the nickel layer than nickel is capable of diffusing into the copper layer. The nickel layer in the overall structure physically separates the copper and the solder. However, it cannot completely block or prevent the diffusion of copper into the solder. Once the solder reaches the molten state, the copper in the nickel layer reacts with the tin-dominated solder and forms the Sn–Ni–Cu intermetallic compound.

The morphology at the interface shown in figure 3a is not characterized by the presence of scallop-like Sn–Cu intermetallic compounds (Chuang *et al* 2004). It includes two sub-layers: (i) A planar looking Sn–Ni–Cu sub-layer, which is adjacent to the nickel layer. (ii) A blocky looking Sn–Ni–Cu sub-layer, which is immediately adjacent to the solder.

**Table 1.** The distribution of key elements in the different layers.

|                    | Sn (%) | Ni (%) | Cu (%) |

|--------------------|--------|--------|--------|

| Ni-layer           | 4.17   | 91.08  | 4.75   |

| Cu-layer           | 2.69   | 1.24   | 96.07  |

| Sn-Ni-Cu compounds | 60.86  | 33.72  | 5.42   |

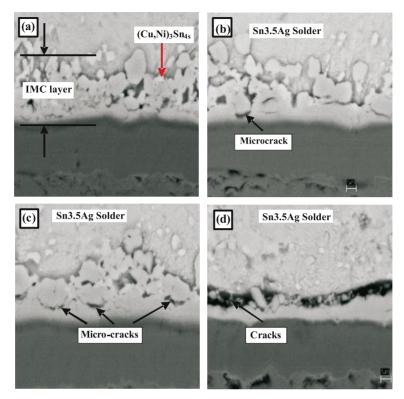

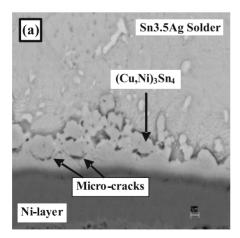

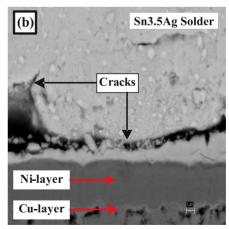

**Figure 4.** Backscattered scanning electron micrographs showing the interfacial structure when subjected to various aging times: (a) 24 h, (b) 48 h, (c) 72 h and (d) 96 h.

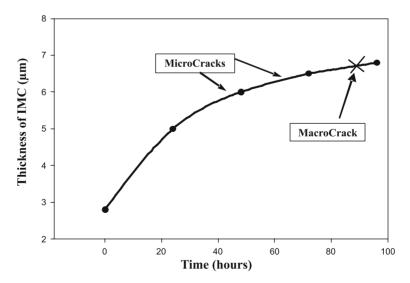

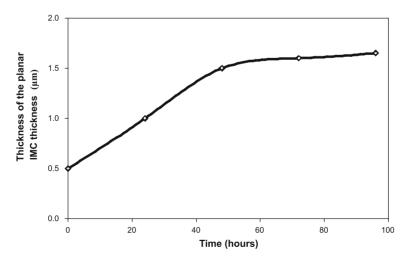

Figure 5. The variation of thickness of the IMC layer as a function of aging time.

| <b>Table 2.</b> The thickness of the IMC as a function of aging time for the Sn solder. |                               |  |  |

|-----------------------------------------------------------------------------------------|-------------------------------|--|--|

|                                                                                         | Thickness (micron meter (μm)) |  |  |

|                |     | Thickness (micron meter (μm)) |      |      |        |  |

|----------------|-----|-------------------------------|------|------|--------|--|

| Solder         | 0 h | 24 h                          | 48 h | 72 h | 96 h   |  |

| Sn3·5Ag solder | 2.8 | 4                             | 6    | 6.5  | cracks |  |

# 3.2 Microstructure of the aged Sn3·5Ag solder bump

The microstructure of the Sn3·5Ag solder bumps on subjecting to a thermal aging treatment at  $150^{\circ}$ C is shown in figure 4. The interfacial structure following 24 h treatment is as shown in figure 4a. To quantify the influence of aging time on microstructure, the thickness of the IMC is measured using the definition shown in figure 3a. The thickness of the IMC was 4 microns ( $\mu$ m) following exposure to the temperature for 24 h and is shown in figure 4a. The thickness of the IMC was 2·8 microns ( $\mu$ m) for the as-solidified case and is shown in figure 3a. Results using the same measurement technique for the other coupons that were aged for 48 h (figure 4b); for 72 h (figure 4c), and for 96 h (figure 4d) are summarised in table 2. The variation of thickness of the IMC as a function of aging time is shown in figure 5. It is observed that the thickness of the IMC increases with an increase in aging time at temperature. Further, it was observed that the highest increase in the thickness of the IMC occurred during the first day or 24 h of aging at the chosen temperature. Following the initial increase there occurs a reduced rate of increase in the thickness of the IMC. After a certain time interval of exposure, the thickness of the IMC cannot increase any further since both microscopic cracks (figure 6a) and macroscopic cracks (figure 6b) appear at the solder/substrate interface.

The presence of fine microscopic cracks along the grain boundaries is caused by a gradual accumulation of stress and resultant strain during aging at the higher temperature. Further, a noticeable difference in the thermal expansion coefficient of the various layers, i.e. copper, nickel and solder causes the microstructure of the Sn–Ag solder that was subjected to aging

**Figure 6.** Scanning electron micrographs identifying the presence and location of the: (a) microscopic cracks, and (b) macroscopic crack.

| Table 3. | Thickness of planar Sn–Ni–Cu sub-layer in the IMC versus aging |

|----------|----------------------------------------------------------------|

| time.    |                                                                |

|                |     | Thickness (micron meter (µm)) |      |      |      |  |

|----------------|-----|-------------------------------|------|------|------|--|

| Solder         | 0 h | 24 h                          | 48 h | 72 h | 96 h |  |

| Sn3·5Ag solder | 0.5 | 1                             | 1.5  | 1.6  | 1.65 |  |

at  $150^{\circ}$ C for 96 h reveals a transformation of the microscopic cracks to occur along the boundary line of the blocky-like compounds and the planar-like looking compounds.

Further, it is seen from figure 4 that the microscopic cracks in the samples that occurred in a region between the planar Sn–Ni–Cu sub-layer and blocky-like non-planar sub-layer of Sn–Ni–Cu, in particular at the root of the blocky sub-layer (see figure 6). The overall thickness of the planar Sn–Ni–Cu sub-layer, measured from figure 3a, figure 4a, figure 4b, figure 4c, and figure 4d, increases with an increase in aging time as summarised in table 3 and shown in figure 7. It was found that the thickness of the planar sub-layer and the whole or entire IMC layer, as a function of aging time at temperature of 150°C, increases with time of exposure to temperature. The macroscopic cracks occurred upon exposing the solder bumps to the high temperature environment 150°C for 96 h aging and are conveniently located along the boundary line, which separates the planar-like and the blocky-like Sn–Ni–Cu intermetallic compound.

#### 4. Conclusions

In this paper, the results of a recent study on understanding the influence of thermal aging, i.e. time of exposure to temperature, on microstructural development of the solder/substrate interface are presented. Based on the exhaustive microscopy examination and the resultant findings the following are the key highlights:

**Figure 7.** Variation of the thickness of the planar Sn–Ni–Cu layer with aging time (hours).

- (i) The interfacial structure between the solder Sn3·5Ag and nickel-coated copper pads includes a layer of the Sn–Cu–Ni intermetallic compound having a planar morphology facing the nickel layer and a blocky structure facing the solder.

- (ii) The thickness of the layer of intermetallic compound for the Sn3·5Ag solder over the Au/Ni/Cu pads increased with an increase in aging time, i.e. time of exposure to temperature. The highest rate of increase was observed to occur during the first 24 h of aging.

- (iii) The macroscopic cracks were found to be present along the boundary of the planar structure and the blocky structure for the Sn3.5Ag solder for the sample that was aged to  $96 \, h$  at a temperature of  $150 \, ^{\circ} C$ .

The authors thank to Mr. Terrance Collier (President of CV Inc) for his continuous guidance and timely assistance during experimental design and subsequent testing. Thanks and appreciation to Mr. Mithun Kuruvilla (Graduate Student; Department of Mechanical Engineering, The University of Akron) for his understanding, timely attention and assistance with formatting the figures.

### References

Andy L 2005 Chip packaging challenges, a roadmap based overview. *Microelectron. Int.* 22(2): 17–20 Chuang T H, Wu H M, Cheng M D, Chang S Y, Yen S F 2004 Mechanisms for interfacial reactions between liquid Sn3·5Sg solders and Cu substrates. *J. Electronic Mater.* 33(1)

Kang S K, Yim M J, Advocate G G Jr., Henderson D W, Gosselin T A, King D E, Konrad J L, Sarkhel A, Puttlitz K J, Shih D Y, Fogel K, Lauro P, Griffin M, Goldsmith C 2002 Interfacial reaction studies on lead (Pb)-free solder alloys. *IEEE Trans. on Electronics Packaging Manuf.* 25(3): 155–161

Lau J H 1995 Flip Chip Technologies. McGraw-Hill companies Inc.

Lau J H, Erasmus S 1993 Review of packaging methods to complement IC performance. *Electronic Packaging and Production* pp 51–56

Ochoa F, Williams J J, Chawla N 2003 The effects of cooling rate on microstructure and mechanical behaviour of Sn-3·5%Ag solder. *J. Metals* pp 56–60

Su P, Korhonen T, Korhonen M, Li C Y 2000 Intermetallic phase formation and growth kinetics at the interface between molten solder and Ni-containing under bump metallization. *Proc. Electronic Components and Technol. Conf.* pp 1712–1718

Tu K N, Gusak A M, Li M 2003 Physics and materials challenges for lead-free solders. *J. Appl. Phys.* 93(3): 1335–1353